# WD1002S-WX2 Winchester Disk Controller OEM Manual

# WESTERN DIGITAL

www.olivettim24.hadesnet.org

Making the leading edge work for you.

WD1002S-WX2 Winchester Disk Controller OEM Manual

# Document No.: 79-000029

2445 McCabe Way Irvine, California 92714 (714) 863-0503 (714) 863-0102 TWX 910-595-1139

July 1985

#### COPYRIGHT © 1985 WESTERN DIGITAL CORP. ALL RIGHTS RESERVED

This document is protected by copyright, and contains information proprietary to Western Digital Corp. Any copying, adaptation, distribution, public performance, or public display of this document without the express written consent of Western Digital Corp. is strictly prohibited. The receipt or possession of this document does not convey any rights to reproduce or distribute its contents, or to manufacture, use, or sell anything that may describe, in whole or in part, without the specific written consent of Western Digital Corp.

# **TABLE OF CONTENTS**

| SECTION 1        | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 1.1       Document Scope.       1-1         1.2       Description       1-1         1.3       Features       1-1         1.4       Operation       1-3         1.4.1       Bi-Directional Control/Data Bus       1-3         1.4.2       Address Decoding Logic       1-3         1.4.3       Configuration Jumpers       1-3         1.4.4       Bios ROM       1-3         1.4.5       WD11C00-17 Logic Array       1-3         1.4.6       WD10C20 Winchester Data Separator and Write       1-3         1.4.7       Sector Buffer RAM       1-3         1.4.8       WD1010A-05 Winchester Disk Controller       1-4         1.4.9       WD1015 Buffer Manager Control Processor       1-4         1.4.10       Reset Logic       1-4 |

| SECTION 2        | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | 2.1       General       2-1         2.2       Electrical       2-1         2.2.1       Host Interface       2-1         2.2.2       Drive Interface       2-1         2.2.3       WD10C20       2-1         2.2.4       Power       2-1         2.3       Physical       2-2         2.4       Environmental       2-2                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SECTION 3        | INTERFACE CONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | 3.1Organization3-13.2Host Interface3-13.3Drive Interface3-23.3.1Drive Control3-23.4Drive Data Connector3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SECTION 4        | INTERFACE TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | 4.1 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>SECTION 5</b> | COMMAND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  | 5.1       General       5-1         5.2       I/O Port Description       5-2         5.2.1       Port 320       5-2         5.2.2       Port 321       5-2         5.2.3       Port 322       5-3         5.2.4       Port 323       5-3         5.3       Command Block       5-3         5.4       Test Drive Ready (Class 0, OP Code 00)       5-4         5.4.1       Possible Error Codes       5-4                                                                                                                                                                                                                                                                                                                                 |

|           |      |                                                                 | - 4   |

|-----------|------|-----------------------------------------------------------------|-------|

|           | 5.5. | Recalibrate (Class 0, OP Code 01)                               |       |

|           |      | 5.5.1 Possible Error Codes                                      | . 5-4 |

|           | 5.6  | Read Status of Last Operation (Class 0, OP Code 03)             |       |

|           | 5.7  | Format Drive Starting at Desired Track (Class 0, OP Code 04)    |       |

|           |      | 5.7.1 Possible Error Codes                                      |       |

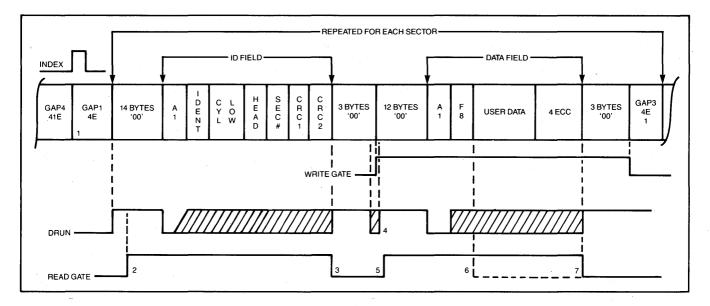

|           |      | 5.7.2 Interleaving                                              |       |

|           | 5.8  | Verify Sectors (Class 0, OP Code 05)                            |       |

|           |      | 5.8.1 Possible Error Codes                                      |       |

|           | 5.9  | Format Track (Class 0, OP Code 06)                              |       |

|           | 5.10 | Format Bad Track (Class 0, OP Code 07)                          |       |

|           | 5.11 | Read Sectors (Class 0, OP Code 08)                              |       |

|           |      | 5.11.1 Possible Error Codes                                     |       |

|           | 5.12 | Write Sectors (Class 0, OP Code 0A)                             |       |

|           |      | 5.12.1 Possible Error Codes                                     |       |

|           | 5.13 | Seek (Class 0, OP Code 0B)                                      |       |

|           |      | 5.13.1 Possible Error Codes                                     |       |

|           | 5.14 | Initialize Drive Parameters (Class 0, OP Code 0C)               |       |

|           | 5.15 | Read ECC Burst Error Length (Class 0, OP Code 0D)               |       |

|           | 5.16 | Read Sector Buffer (Class 0, OP Code 0E)                        |       |

|           | 5.17 | Write Sector Buffer (Class 0, OP Code 0F)                       |       |

|           | 5.18 | Execute Sector Buffer Diagnostic (Class E, OP Code 00)          |       |

|           |      | 5.18.1 Possible Error Codes                                     |       |

|           | 5.19 | Execute Drive Diagnostic (Class E, OP Code 03).                 |       |

|           |      | 5.19.1 Possible Error Codes                                     |       |

|           | 5.20 | Controller Diagnostics (Class E, OP Code 04)                    |       |

|           |      | 5.20.1 WD1010A-05 Test                                          |       |

|           |      | 5.20.2 WD11C00-17 ECC Test                                      |       |

|           |      | 5.20.3 Sector Buffer Test.                                      |       |

|           |      | 5.20.4 WD1015 RAM Test                                          |       |

|           |      | 5.20.5 WD1015 ROM Test                                          |       |

|           |      | 5.20.6 Possible Error Codes                                     |       |

|           | 5.21 | Read Long (Class E, OP Code 05)                                 |       |

|           |      | 5.21.1 Possible Error Codes                                     |       |

|           | 5.22 | Write Long (Class E, OP Code 06)                                |       |

|           |      | 5.22.1 Possible Error Codes                                     | 5-11  |

|           |      |                                                                 |       |

| SECTION 6 | THE  | DRY OF OPERATION                                                |       |

|           | 6.1  | General                                                         | 6-1   |

|           | 6.2  | Buses                                                           | 6-1   |

|           |      | 6.2.1 Host Interface Address Bus A0 through A19.                | 6-1   |

|           |      | 6.2.2 Host Interface Data/Command Bus D0 through D7             | 6-1   |

|           |      | 6.2.3 WD1002S-WX2 Intraboard Command/Status Bus BD0 through BD7 | 6-1   |

|           |      | 6.2.4 WD1002S-WX2 Intraboard Command/Data Bus AD0 through AD7   |       |

|           |      | 6.2.5 WD1002S-WX2 Intraboard Address Bus RA0 through RA10       |       |

|           | 6.3  | Bus Protocol                                                    |       |

|           |      | 6.3.1 Selection Phase                                           | . 6-3 |

|           |      | 6.3.2 Command Phase                                             |       |

|           |      | 6.3.3 Data Phase.                                               |       |

|           |      | 6.3.3.1 Programmed I/O Data Transfer                            |       |

|           |      | 6.3.3.2 DMA Data Transfer                                       |       |

|           |      |                                                                 |       |

| 6.4  | Device Address Decoder                         |

|------|------------------------------------------------|

| 6.5  | Bios ROM                                       |

| 6.6  | Configuration Jumpers                          |

| 6.7  | WD11C00-17 Logic Array                         |

|      | 6.7.1 Status, Read, and Write Ports            |

|      | 6.7.2 Sector Buffer RAM Addressing and Control |

|      | 6.7.3 ECC Circuitry                            |

|      | 6.7.4 Reset Timing Circuitry                   |

| 6.8  | WD1015 Buffer Manager Control Processor        |

|      | 6.8.1 Exception Handling 6-6                   |

| 6.9  | Sector Buffer                                  |

| 6.10 | WD1010A-05 Winchester Disk Controller          |

| 6.11 | WD10C20 Self-Adjusting Data Separator          |

|      | 6.11.1 Clock Generator                         |

|      | 6.11.2 Write Precompensation Circuit           |

|      | 6.11.3 Data Separator                          |

|      |                                                |

# SECTION 7 INSTALLATION

| 7.1 | Hardware and Software Installation | 7-1 |

|-----|------------------------------------|-----|

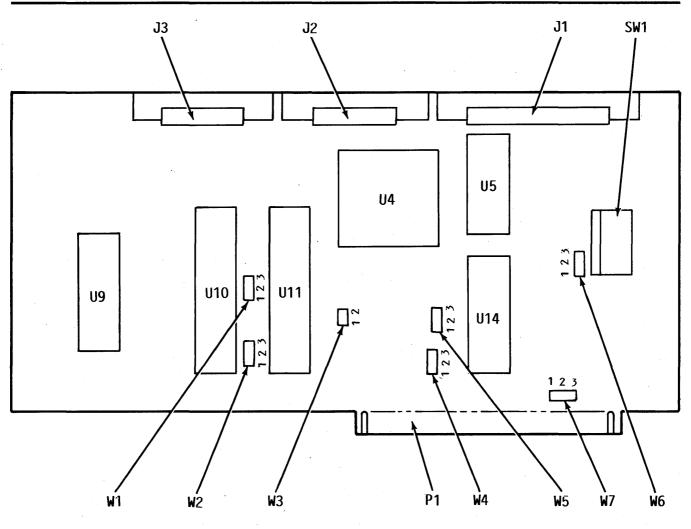

| 7.2 | Jumper Installation and Locations  | 7-1 |

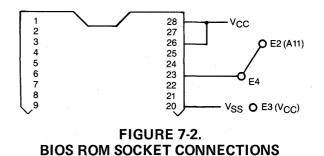

| 7.3 | Bios ROM Installation              | 7-3 |

# LIST OF TABLES

| TABLE | TITLE                                         | GE   |

|-------|-----------------------------------------------|------|

| 1-1   | WD1015 Description                            | 1-4  |

| 3-1   | Host Interface Connector (P1) Pin Description |      |

| 3-2   | Drive Control Connector (J1) Pin Description. | 3-3  |

| 3-3   | Drive Data Connectors – J2, J3                | 3-5  |

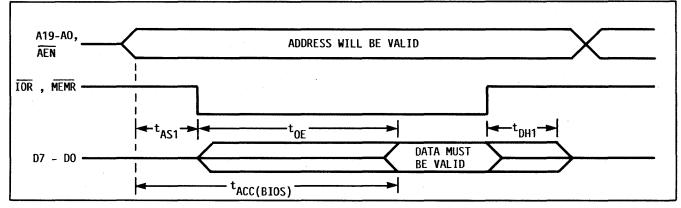

| 4-1   | Host I/O or BIOS Read Timing                  | 4-1  |

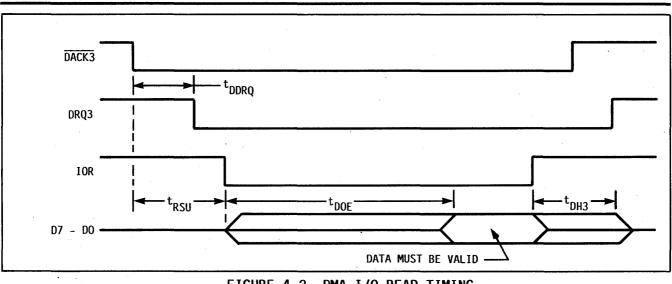

| 4-2   | DMA I/O Read Timing                           |      |

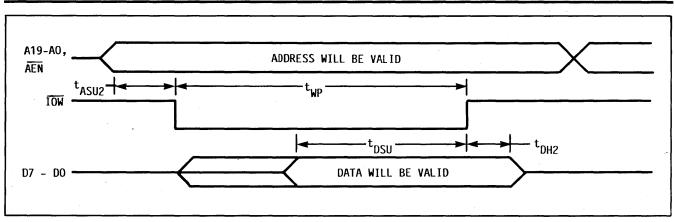

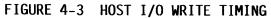

| 4-3   | Host I/O Write Timing.                        |      |

| 4-4   | DMA I/O Write Timing                          |      |

| 5-1   | Command Summary                               | 5-1- |

| 5-2   | I/O Port Descriptions                         |      |

| 5-3   | Hardware Status                               |      |

| 5-4   | Stepping Rate Codes                           |      |

| 5-5   | Controller Returned Error Codes               |      |

| 7-1   | Jumper Selectable Options (W1 through W5)     | 7-1  |

| 7-2   | SW1 Jumper Block Description                  | 7-2  |

# LIST OF ILLUSTRATIONS

| FIGURE | TITLE PA                             | AGE   |

|--------|--------------------------------------|-------|

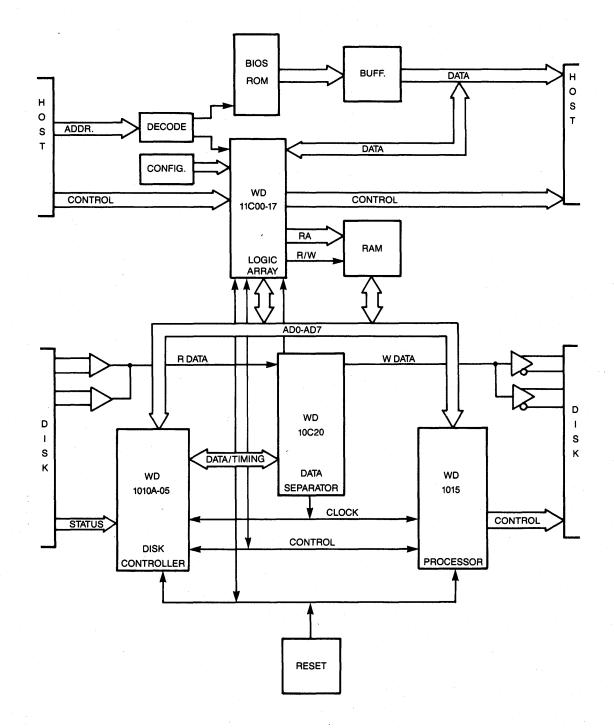

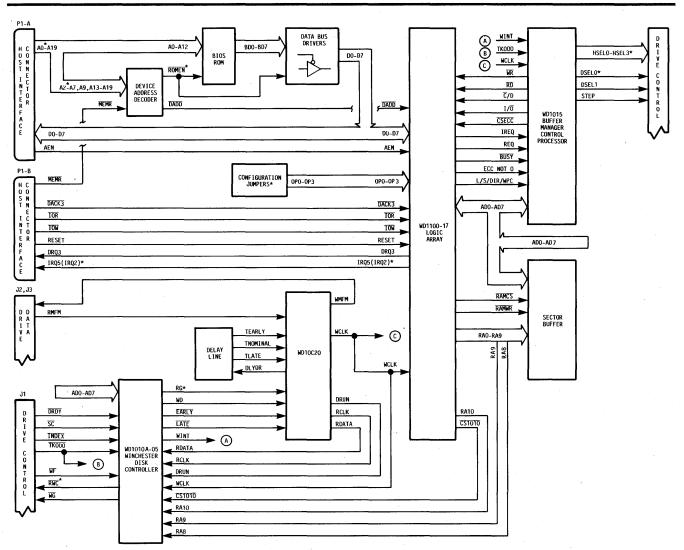

| 1-1    | WD1002S-WX2 Functional Block Diagram | . 1-2 |

| 4-1    | Host I/O or BIOS Read Timing         | . 4-1 |

| 4-2    | DMA I/O Read Timing                  | . 4-2 |

| 4-3    | Host I/O Write Timing.               | . 4-3 |

| 4-4    | DMA I/O Write Timing                 | . 4-4 |

| 5-1    | Command Block Description.           | . 5-3 |

| 5-2    | Four Status Bytes                    |       |

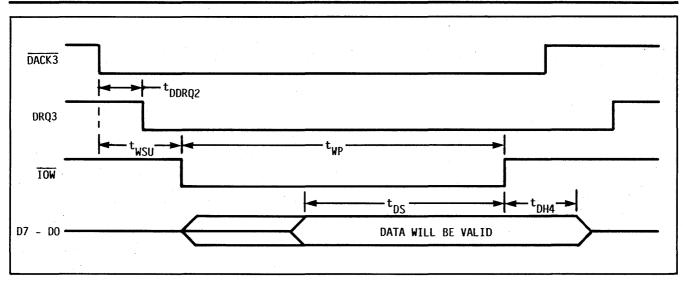

| 5-3    | Format                               | . 5-7 |

| 5-4    | 17 Sectors with a 3.1 Interleave     | . 5-8 |

| 6-2    | WD1002S-WX2 Detailed Block Diagram   | . 6-2 |

| 7-1    | Jumper Locations                     | . 7-3 |

| 7-2    | Bios Rom Socket Connections          |       |

SECTION I INTRODUCTION

#### 1.1 DOCUMENT SCOPE

This document provides the user with the information required to design related software drivers and interface connections for efficient use of the WD1002S-WX2 Winchester Disk Controller Board. It is to the user's advantage to become familiar with the following related documents:

WD11C00-17 Logic Array..... Data Sheet WD10C20 Winchester Data Separator and

Write Precompensation Device ..... Data Sheet WD1010-05 Winchester Disk

Controller ..... Data Sheet WD1010 Winchester Disk

Controller ..... Application Note WD1015 Buffer Manager Control

Processor..... Data Sheet ST-506 Micro Winchester Disk Interface..... ST506

Seagate Technology Scotts Valley, Cal.

#### 1.2 DESCRIPTION

The WD1002S-WX2 is a stand-alone, general purpose Winchester Disk Controller. The WD1002S-WX2 interfaces up to two Winchester Disk drives and a Host Processor, e.g. an IBM XT.

The Winchester interface conforms to the Seagate Technology ST506 interface. All necessary receivers and drivers are included on the board, allowing direct connection to the disk drive(s).

A separate computer access port enables communications between the Host and disk controller. An 8-bit bi-directional bus and appropriate control signals comprise this port. Disk read or write data, status information, and command parameters are transferred via this bus. An on-board data buffer allows bus transfers to be executed independently of the drive's data transfer.

The WD1002S-WX2 is based on a proprietary chip set consisting of the WD11C00-17, WD1010A-05, WD10C20, and WD1015.

#### 1.3 FEATURES

- 8-BIT BI-DIRECTIONAL BUS HOST

INTERFACE

- IBM XT WINCHESTER CONTROLLER EMULATION, IBM PC HOST INTERFACE

- WD10C20 WINCHESTER DATA SEPARATOR AND WRITE PRECOMPENSATION DEVICE

- WD11C00-17 LOGIC ARRAY

- DATA RATES UP TO 5 MBITS/SEC

- CONTROLS UP TO 2 DRIVES USING SEAGATE TECHNOLOGY ST506

- SUPPORTS DRIVES OF ANY CONFIGURATION UP TO 1024 CYLINDERS AND 16 R/W HEADS WITH THE WD1015-24 OR 8 R/W HEADS WITH THE WD1015-14

- THE CONTROLLED DRIVES NEED NOT BE OF THE SAME CAPACITY OR CONFIGURATION

- ERROR CORRECTION ON DATA FIELD ERRORS, CRC ID FIELD VERIFICATION

- 32 BIT ECC POLYNOMIAL FOR ERROR DETECTION AND CORRECTION

- READ AND WRITE LONG COMMANDS FOR CHECKING ERROR CORRECTION CIRCUITRY

- SELECTABLE AUTOMATIC RETRIES ON ALL ERRORS

- AUTOMATIC RESTORE AND RE-SEEK ON ALL SEEK ERRORS

- AUTOMATIC FORMATTING

- 512 BYTES PER SECTOR

- SECTOR INTERLEAVE CAPABILITY

- MULTIPLE SECTOR READS AND WRITES

- OVERLAPPED SEEK CAPABILITY ON BUFFERED-STEP DRIVES

- SUPPORTS IMPLIED SEEKS ON ALL COMMANDS

- INTERNAL DIAGNOSTICS

- DMA TRANSFER CAPABILITY

- SUPPORTS INTERRUPTS, INTERRUPT REQUESTS, AND DMA REQUEST SHARING

- INCLUDES SOCKET FOR USER SUPPLIED 2716, 2732, OR 2764 ROM

- BIOS AVAILABLE

## 1.4 OPERATION

This section provides an operational overview of the WD1002S-WX2 Winchester Disk Controller. For a detailed explanation, refer to Section 6 (Theory of Operation). As illustrated in Figure 1-1, the WD1002S-WX2 consists of the following components:

Bi-directional Control/Data Bus Address Decoding Logic Configuration Switches Basic Input/Output System (BIOS) ROM WD11C00-17 WD10C20 Sector Buffer RAM WD1010A-05 WD1015 Reset Logic

#### 1.4.1 BI-DIRECTIONAL CONTROL/DATA BUS

The 8-bit, bi-directional bus transmits addresses, commands, data, and status information. This bus links the WD1002S-WX2 to the Host. Specifically, this bus transmits data between the Host and Sector Buffer RAM.

#### **1.4.2 ADDRESS DECODING LOGIC**

The puspose of this logic is to decode a valid device address from the Host.

#### **1.4.3 CONFIGURATION JUMPERS**

These jumpers configure the WD1002S-WX2 for different disk drive capacities.

#### 1.4.4 BIOS ROM

The Host, after powering up, interrogates its ports to determine what devices are connected. The Host uses information supplied by the BIOS ROM to perform an install operation. Then, during normal operation, the BIOS operates much like a driver that is resident in the Host's memory space. The BIOS ROM is addressed at Host memory locations C8000-C8FFF. The BIOS is addressed by the A0 through A19 bus. Outputs to the Host are via the Intraboard Command/Status bus (BD0 through BD7) and Host Interface Data/Command bus (D0 through D7).

#### 1.4.5 WD11C00-17

The WD11C00-17 incorporates several functions in a single package. Implementation of these functions occurs by combining random logic and specialized circuits. The WD11C00-17 contains the following circuits:

Status ports

Read and write ports

Sector Buffer RAM addressing and control ECC

Reset timing

The WD11C00-17 connects directly to the Host Interface Data/Command and Intraboard Command/Data (AD0-AD7) buses.

#### 1.4.6 WD10C20

The WD10C20 performs phase-locked loop data synchronization on read data from the Winchester drives. This device also conditions write data to be recorded on the disk. The WD10C20 includes both frequency and phase detection. Zero phase error start-up circuitry eliminates problems due to asymmetry. The WD10C20 requires no adjustments and contains all data synchronization and write precompensation circuitry in a single device.

#### **1.4.7 SECTOR BUFFER RAM**

The Sector Buffer RAM is a 2K x 8 RAM. The Sector Buffer allows Host data transfers independent of the actual drive data transfer rate. The Sector Buffer temporarily stores the following information:

Sector data during Read and Write Commands Disk format information during a Format Command

Drive characteristics during a Set Parameters Command

# FIGURE 1-1. WD1002S-WX2 FUNCTIONAL BLOCK DIAGRAM

#### 1.4.8 WD1010A-05

The primary function of the WD1010A-05 is to control data transfers between the disk and the Sector Buffer. Data transfers take place after the WD1015 Buffer Manager Control Processor positions the selected head over the desired track. The WD1010A-05 receives the parameters and commands from the WD1015 via the AD0 through AD7 bus. The WD1010A-05 interprets the parameter or command, determines which sectors are involved, and whether a read, write, or format function is required.

## 1.4.9 WD1015

The WD1015 manages and controls all commands and communications between the Host and WD1010A-05. The WD1015 controls ECC and CRC functions.

There are two versions of the WD1015. Table 1-1 describes the differences between the two versions of the WD1015. The acronym WD1015 refers to both versions. When a specific reference is made to a specific version, the appropriate acronym is used.

| FUNCTION                                                               | WD1015-14 | WD1015-24  | REMARKS                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Execution of automatic<br>self-test after Reset<br>command or power-up | Yes       | No         |                                                                                                                                                                                                                                                                                  |

| Supports 16 heads                                                      | No        | Yes        | The WD1015-14 supports up to eight heads.<br><u>The WD1015-14</u> uses the REDUCED WRITE<br>CURRENT (RWC) signal. The WD1015-24<br>supports up to 16 heads. The WD1015-24<br>uses the RWC pin on J1 as HEAD SELECT 3<br>(HS3). Refer to Sections 3 and 7 for further<br>details. |

| 3.5 seconds time-out on single track steps                             | No        | Yes        | 3.5 seconds time-out allows removable/servo drives time to create servo map. WD1015-14 allows 1 second.                                                                                                                                                                          |

| Bit 4 of opcode in<br>Command Control                                  | Valid     | Don't care | Refer to Section 5 for further details.                                                                                                                                                                                                                                          |

| Step rates                                                             |           |            | Refer to Section 5 for further details.                                                                                                                                                                                                                                          |

| Format Bad Track                                                       |           |            | Refer to Section 5 for further details.                                                                                                                                                                                                                                          |

#### TABLE 1-1. WD1015 DESCRIPTION

#### 1.4.10 RESET LOGIC

The Reset Logic initializes the internal circuitry of the WD1002S-WX2 during the power-up process or a low voltage condition. The Reset Logic also <u>disables the WRITE GATE</u> signal. Disabling WRITE GATE prevents writing spurious data to the disk drive during power up, power down or a low voltage condition.

# SECTION II SPECIFICATIONS

# 2.1 GENERAL

This section contains the overall specifications for the WD1002S-WX2 Winchester Disk Controller.

## 2.2 ELECTRICAL

#### 2.2.1 HOST INTERFACE

Type Max Cable Length

## 2.2.2 DRIVE INTERFACE

Encoding Method Cylinders per Drive Sectors per Track Bytes per Sector Heads

Drive Selects Stepping Rates

Data Transfer Rate Write Precomp Time Sectoring CRC Polynomial ECC Polynomial

Reciprocal ECC Polynomial

Miscorrection Prob. Non-detection Prob. Correction Span Max Cable Length: Control (Total Daisy Chain) Data (Radial-each)

# 2.2.3 WD10C20

Acquisition Time Capture Range Bit Jitter Tolerance Asymmetry Tolerance

### 2.2.4 **POWER**

Voltage Current Ripple Voltage Current IBM PC

Connects directly to Host motherboard with a 62 pin card edge connector

MFM Up to 1024 17 512 8 with WD1015-14 16 with WD1015-24 2 70µsec, 200µsec, 3msec (WD1015-14) 18 µsec, 30 µsec, 45µsec, 60µsec, 75µsec, 210µsec, 3msec (WD1015-24) 5Mbits/sec (ST506) 12nsec Soft  $X^{16} + X^{12} + X^5 + 1$  $X^{32} + X^{28} + X^{26} + X^{19} +$  $X^{17} + X^{10} + X^6 + X^2 + 1$  $X^{32} + X^{30} + X^{26} + X^{22} +$  $X^{15} + X^{13} + X^6 + X^4 + 1$ 5 bit correction = < 1.6 E-5<2.3 E-10 Up to 11-bit burst

3 meters (10 ft.) 3 meters (10 ft.)

< or = 12.8 $\mu$ s ± 2.2% to 1ns after 12.8 $\mu$ s acquisition ± -34ns (min. of 40 db after acquisition) 34ns (write precompensation turned off; as measured over constant RCLK pattern)

5V ±5% 0.8 amps max. 0.1 volts max., 25 mV typical +12V ±10% 10 mA. max.

# 2.3 PHYSICAL

Form factor Length Width Height (max. including board, components & leads)

IBM PC 20.6 centimeters (8.1 inches) 9.78 centimeters (3.85 inches) 1.27 centimeters (0.50 inches)

# 2.4 ENVIRONMENTAL

Ambient Temperature Relative Humidity Altitude Air Flow MTBF MTTR 0°C (32°F) to 55°C (131°F) 10% to 95% non-condensing 0 to 3000 meters (10,000 ft.) 100 lin ft/min. at 0.5" from component surfaces. 10,000 POH 30 Minutes

# SECTION III INTERFACE CONNECTIONS

# 3.1 ORGANIZATION

The WD1002S-WX2 has four on-board connectors for user application.

- P1 Host interface: 62 pin IBM PC compatible card edge connector.

- J1 Drive control: 34 pin dual row header connector daisy-chained to two drives. The control signals at the second drive from the WD1002S-WX2 (no more than a total length of 3 meters or 10 feet) are terminated with a 220 ohm resistor to +5V and a 330 ohm

resistor to ground.

J2, J3 Drive data: 20 pin dual row header connectors, radially connected each to its own drive.

#### 3.2 HOST INTERFACE

Connector P1 pins A1 through A31 are on the component side of the board and B1 through B31 are on the artwork side. Table 3-1 describes the Host interface connector (P1) pin assignments and functions.

| TABLE 3-1. HOST INTERFACE CONNECTOR (P1) | PIN DESCRIPTION |

|------------------------------------------|-----------------|

|------------------------------------------|-----------------|

| PIN<br>NUMBER      | MNEMONIC          | SIGNAL NAME                     | 1/0 | FUNCTION                                                                                                                                                                                                                                                                            |

|--------------------|-------------------|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                 |                   | Not Connected                   |     |                                                                                                                                                                                                                                                                                     |

| A2<br>thru<br>A9   | D7<br>thru<br>D0  | DATA 7<br>thru<br>DATA 0        | 1/0 | 8-Bit, tri-state, bi-directional bus. It is used to<br>transmit data between the Host and Sector Buffer,<br>the Command Block to the WD1015, status and<br>drive configuration to the Host. The BIOS trans-<br>mits parameter information and commands to<br>the Host via this bus. |

| A10                |                   | Not Connected                   |     |                                                                                                                                                                                                                                                                                     |

| A11                | AEN               | ADDRESS<br>ENABLE               | I   | AEN is asserted during a DMA mode of operation<br>making the I/O ports 320 hex thru 323 hex<br>inaccessible to the Host. Data transfers and intra-<br>bus control is initiated by asserting DACK3. The<br>BIOS ROM can still be addressed via A0-A19.                               |

| A12<br>thru<br>A31 | A19<br>thru<br>A0 | ADDRESS BUS<br>A19 thru A0      |     | A0 thru A9 are used during programmed I/O<br>mode of operation to address ports 320 hex thru<br>323 hex. They are inhibited during DMA by<br>AEN. A0 thru A19 addresses the BIOS ROM<br>regardless of the state of AEN.                                                             |

| B1                 | GND               | GROUND                          | -   |                                                                                                                                                                                                                                                                                     |

| B2                 | RST               | RESET                           |     | When asserted, RST places the WD1002S-WX2 into its initial power-up state.                                                                                                                                                                                                          |

| B3                 | +5VDC             | +5VDC                           |     | +5VDC                                                                                                                                                                                                                                                                               |

| B4                 | IRQ2              | INTERRUPT<br>REQUEST<br>LEVEL 2 | 0   | The WD1002S-WX2 asserts IRQ2 to interrupt the<br>Host upon the completion of a command. Use of<br>IRQ2 is jumper selectable. Use of IRQ5 is stan-<br>dard. Refer to Section 7 for further details on<br>jumper selectable options.                                                  |

| B5<br>thru<br>B8   |                   | Not Connected                   |     |                                                                                                                                                                                                                                                                                     |

| В9                 | +12VDC            | +12VDC                          |     | +12VDC                                                                                                                                                                                                                                                                              |

| B10                | GND               | GROUND                          |     |                                                                                                                                                                                                                                                                                     |

| B11                |                   | Not Connected                   |     |                                                                                                                                                                                                                                                                                     |

| TABLE 3-1. HOST INTERFACE CONNECTOR (P1) PIN DESCRIPTION (CONT'D.) |          |                                 |             |                                                                                                                                                                       |  |  |  |

|--------------------------------------------------------------------|----------|---------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN<br>NUMBER                                                      | MNEMONIC | SIGNAL NAME                     | 1/0         | FUNCTION                                                                                                                                                              |  |  |  |

| B12                                                                | MEMR     | MEMORY<br>READ                  | ., <b>I</b> | The Host, to read the BIOS ROM places the address on A0 thru A19, asserts MEMR and receives the data via D0 thru D7 data bus.                                         |  |  |  |

| B13                                                                | IOW      | I/O WRITE                       | 1           | The Host or DMA controller asserts IOW when a data byte is to be written to the WD1002S-WX2.                                                                          |  |  |  |

| B14                                                                | IOR      | I/O READ                        | 1           | The Host or DMA controller asserts IOR when a data or status byte is to be read from the WD1002S-WX2.                                                                 |  |  |  |

| B15                                                                | DACK3    | DMA<br>ACKNOWLEDGE<br>CHANNEL 3 | ι, η        | The DMA controller asserts DACK3 in response<br>to DRO3 sent by the WD1002S-WX2. DACK3<br>enables DMA data transfer, bypassing port 320<br>which was disabled by AEN. |  |  |  |

| B16                                                                | DRQ3     | DMA REQUEST<br>CHANNEL 3        | 0           | WD1002S-WX2 asserts DRO3 to inform the DMA controller that data is available for transfer.                                                                            |  |  |  |

| B17<br>thru<br>B22                                                 |          | Not Connected                   | :<br>-      |                                                                                                                                                                       |  |  |  |

| B23                                                                | IRQ5     | INTERRUPT<br>REQUEST<br>LEVEL 5 | 0           | The WD1002S-WX2 asserts IRQ5 to interrupt the Host upon the completion of a command.                                                                                  |  |  |  |

| B24<br>thru<br>B28                                                 |          | Not Connected                   |             |                                                                                                                                                                       |  |  |  |

| B29                                                                | +5VDC    | +5VDC                           |             | +5VDC                                                                                                                                                                 |  |  |  |

| B30                                                                |          | Not Connected                   |             |                                                                                                                                                                       |  |  |  |

| B31                                                                | GND      | GROUND                          |             |                                                                                                                                                                       |  |  |  |

CONNECTOR (D1) DIN DECODIDITION (CONTO)

# 3.3 DRIVE INTERFACE

TADIE 24

1100

# 3.3.1 DRIVE CONTROL

Control signals are common to all drives and are daisy-chained to the drives from a single connector, J1. To terminate the control signals properly, the last drive in the daisy-chain must have a 220/330 ohm resistor pack installed. Table 3-2 describes the drive control connector (J1) pin assignments and functions.

|              |             | TABLE 3-2. D | RIVE CONTROL CON                            | NECT         | OR (J1) PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|-------------|--------------|---------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIG.<br>GND. | SIG.<br>PIN | MNEMONIC     | SIGNAL<br>NAME                              | 1/0          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1            | 2           | RWC/HS3      | REDUCE<br>WRITE<br>CURRENT/HEAD<br>SELECT 3 | Ο            | The WD1015-14 allows this pin to be used<br>as the $\overline{RWC}$ pin. The WD1015-24 uses this<br>pin as $\overline{HS3}$ . Refer to Section 7 for further<br>details. $\overline{RWC}$ is used by the drive to reduce<br>the write current on the inner cylinders.<br>This lessens the bit shift caused by the<br>greater bit density on these cylinders. $\overline{RWC}$<br>is asserted when the specified cylinder is<br>reached. $\overline{HS3}$ is one of four Head Select<br>signals decoded by the drive to select one<br>of 16 R/W heads. |

| 3            | 4           | HS2          | HEAD<br>SELECT 2                            | 0            | $\overline{\text{HS2}}$ is one of three (or four) Head Select signals decoded by the drive to select one of eight (or 16) R/W heads.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5            | 6           | WG           | WRITE GATE                                  | 0            | $\overline{\text{WG}}$ is asserted when valid data is to be<br>written. It is used by the drive to enable<br>the write current to the head. WD1002S-<br>WX2 de-asserts this signal when a $\overline{\text{WF}}$ is<br>detected. Circuitry is included to ensure<br>the output does not glitch during power<br>on, power down or power failure.                                                                                                                                                                                                       |

| 7            | .8          | SC           | SEEK<br>COMPLETE                            | 1            | SC informs the WD1002S-WX2 that the selected head has reached the desired cylinder and has stabilized. Since SC is not checked after a Seek Command, overlapped seeks are allowed.                                                                                                                                                                                                                                                                                                                                                                    |

| 9            | 10          | ТК000        | TRACK 000                                   | · 1          | The drive asserts this signal when the heads are positioned over the outermost cylinder, cylinder 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11           | 12          | WF           | WRITE FAULT                                 | <b>I</b> * • | $\overline{WF}$ is asserted by the drive when a write error occurs. The command in progress aborts and no other command can be executed while this signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                |

| 13           | 14          | HSO          | HEAD<br>SELECT 0                            | 0            | HSO is one of three (or four) Head Select<br>signals decoded by the drive to select one<br>of eight (or 16) R/W heads.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15           | 16          | GND          | GROUND<br>Not Connected                     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17           | 18          | HS1          | HEAD<br>SELECT 1                            | 0            | HS1 is one of three (or four) Head Select<br>signals decoded by the drive to select one<br>of eight (or 16) R/W heads.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19           | 20          | INDEX        | INDEX PULSE                                 | ]            | This signal indicates the start of a track.<br>It is used as a synchronization point during<br>formatting and as a time out mechanism<br>for retries. This signal pulses once for each<br>revolution of the disk.                                                                                                                                                                                                                                                                                                                                     |

TABLE 3-2. DRIVE CONTROL CONNECTOR (J1) PIN DESCRIPTION

|                  | TABLE 3-2. DRIVE CONTROL CONNECTOR (J1) PIN DESCRIPTION (CONT'D.) |          |                   |     |                                                                                                                                                                                                                                                |  |  |

|------------------|-------------------------------------------------------------------|----------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SIG.<br>GND.     | SIG.<br>PIN                                                       | MNEMONIC | SIGNAL<br>NAME    | I/O | DESCRIPTION                                                                                                                                                                                                                                    |  |  |

| 21               | 22                                                                | DRDY     | DRIVE READY       | l   | The drive asserts this signal when the motor<br>is up to speed. No Read or Write com-<br>mands can be performed if this signal is<br>not asserted.                                                                                             |  |  |

| 23               | 24                                                                | STEP     | STEP PULSE        | 0   | STEP, along with DIRIN, positions the<br>heads to the desired cylinder. STEP pulses<br>the stepping motor at the rate specified by<br>the SP bits in the Command Block and is<br>controlled by the WD1015. DIRIN spec-<br>ifies the direction. |  |  |

| 25               | 26                                                                | DSEL 0   | DRIVE<br>SELECT 0 | 0   | $\overrightarrow{\text{DSEL 0}}$ is the decoded output of the SDH Register within the WD1010A-05, latched and sent to the drive by the WD1015 to select drive 0.                                                                               |  |  |

| 27               | 28                                                                | DSEL 1   | DRIVE<br>SELECT 1 | 0   | $\overrightarrow{\text{DSEL 1}}$ is the decoded output of the SDH Register within the WD1010A-05, latched and sent to the drive by the WD1015 to select drive 1.                                                                               |  |  |

| 29<br>thru<br>32 |                                                                   |          | Not Connected     |     |                                                                                                                                                                                                                                                |  |  |

| 33               | 34                                                                | DIRIN    | DIRECTION IN      | 0   | DIRIN determines the direction the R/W<br>heads take when stepped. Asserted = in,<br>de-asserted = out.                                                                                                                                        |  |  |

# .

# 3.4 DRIVE DATA CONNECTOR

The data is differential in nature and must be connected to each drive with its own cable, drive 0 to J2 and drive 1 to J3. It should be a flat ribbon cable, or twisted pair, less than 3 meters (10 feet) in length. The connector is a 20 pin vertical header on 0.25 centimeter (0.1 inch) center. Table 3-3 describes the drive data connectors (J2 and J3) pin assignments and functions.

| SIG.<br>GND. | SIG.<br>PIN | I/O | SIGNAL NAME      |

|--------------|-------------|-----|------------------|

|              | 1           |     | NC               |

| 2            |             |     | GND              |

|              | 3           |     | NC               |

| 4            |             |     | GND              |

|              | 5           |     | NC               |

| 6            |             |     | GND              |

|              | 7           |     | NC               |

| 8            |             |     | GND              |

|              | 9           |     | NC               |

|              | 10          |     | NC               |

| 11           |             |     | GND              |

| 12           |             |     | GND              |

|              | 13          | 0   | + MFM Write Data |

|              | 14          | 0   | – MFM Write Data |

| 15           |             |     | GND              |

| 16           |             |     | GND              |

|              | 17          |     | + MFM Read Data  |

|              | 18          |     | – MFM Read Data  |

| 19           |             |     | GND              |

| 20           |             |     | GND              |

TABLE 3-3. DRIVE DATA CONNECTORS - J2, J3

# SECTION IV INTERFACE TIMING

# 4.1 <u>TIMING</u>

Timing diagrams are shown in Figures 4-1 through 4-4 and their values are listed in Tables 4-1 through 4-4 respectively. Since the Controller I/O ports can be accessed by either the Host system DMA Controller or the Host processor, timing is given for both cases. The processor executes I/O and memory reads from the ports and the on-board BIOS ROM, and writes to the ports. DMA is used for data transfers between the data I/O port and the Host RAM.

FIGURE 4-1 HOST I/O OR BIOS READ TIMING

TABLE 4-1 HOST I/O OR BIOS READ TIMING

| SYMBOL           | CHARACTERISTIC             | MIN. | MAX. |

|------------------|----------------------------|------|------|

| t <sub>AS1</sub> | Address Setup Time         | 50   |      |

| tACC             | Address Access Time (BIOS) |      | 250  |

| t <sub>OE</sub>  | Output Enable Time         |      | 175  |

| t <sub>DH1</sub> | Data Hold Time             | 0    |      |

NOTE: All units in Table 4-1 are in nsec.

4-1

FIGURE 4-2 DMA I/O READ TIMING

| Table 4-2 DMA I/O READ TIMING | Table | 4-2 | DMA | I/0 | READ | TIMING |

|-------------------------------|-------|-----|-----|-----|------|--------|

|-------------------------------|-------|-----|-----|-----|------|--------|

| SYMBOL            | CHARACTERISTIC       | MIN. | MAX. |

|-------------------|----------------------|------|------|

| t <sub>DDRQ</sub> | DRQ3 De-assert Delay | 20   | 45   |

| t <sub>RSU</sub>  | Read Setup Time      | 7    |      |

| tDOE              | Data Output Enable   |      | 175  |

| t <sub>DH3</sub>  | Data Hold Time       | 0    |      |

NOTE: All units in Table 4-2 are in nsec.

TABLE 4-3 HOST I/O WRITE TIMING

| SYMBOL            | CHARACTERISTIC         | MIN. |

|-------------------|------------------------|------|

| t <sub>ASU2</sub> | Address Setup Time     | 50   |

| t <sub>WP</sub>   | Write Pulse Time (I/O) | 100  |

| t <sub>DSU</sub>  | Data Setup Time        | 50   |

| t <sub>DH2</sub>  | Data Hold Time         | 0    |

NOTE: All units in Table 4-3 are in nsec.

FIGURE 4-4 DMA I/O WRITE TIMING

TABLE 4-4 DMA I/O WRITE TIMING

| BLE 4-4 DMA I/O WRITE TIMING |                      |      |      |  |  |  |  |  |

|------------------------------|----------------------|------|------|--|--|--|--|--|

| SYMBOL                       | CHARACTERISTIC       | MIN. | MAX. |  |  |  |  |  |

|                              | DRQ3 De-assert Delay | 20   | 45   |  |  |  |  |  |

| twsu                         | Write Setup Time     | 7    |      |  |  |  |  |  |

| t <sub>WP</sub>              | Write Pulse Width    | 100  |      |  |  |  |  |  |

| t <sub>DS</sub>              | Data Setup Time      | 50   |      |  |  |  |  |  |

| <sup>t</sup> DH4             | Data Hold Time       | 0    |      |  |  |  |  |  |

NOTE: All units in Table 4-4 are in nsec.

# SECTION V COMMAND DESCRIPTION

# 5.1 GENERAL

This section provides a detailed description of the Command Block format and function of the 19 commands supported by the WD1002S-WX2. Fourteen of the commands are operational and five are diagnostic. An explanation of how the commands perform their function is discussed in Section 6 Theory of Operation. Table 5-1 lists a summary of the commands.

|                                     | PARAMETERS (Refer to Figure 5-1) |     |    |     |     |         |    |    |      |

|-------------------------------------|----------------------------------|-----|----|-----|-----|---------|----|----|------|

| COMMAND                             | OP CODE                          | DRV | HD | CYL | SEC | BLK/INT | R1 | R2 | STEP |

| TEST DRIVE READY                    | 00                               | V   | n  | n   | n   | n       | n  | n  | n    |

| RECALIBRATE                         | 01                               | V   | n  | n   | n   | n       | V  | n  | n    |

| READ STATUS OF<br>LAST OPERATION    | 03                               | V   | n  | n   | n   | n       | n  | n  | n    |

| FORMAT DRIVE                        | 04                               | V   | V  | V   | DR  | V (INT) | V  | n  | V    |

| VERIFY SECTORS                      | 05                               | V   | V  | V   | V   | V (BLK) | V  | V  | V    |

| FORMAT TRACK                        | 06                               | V   | V  | V   | DR  | V (INT) | V  | n  | V    |

| FORMAT BAD TRACK                    | 07                               | V   | V  | - V | DR  | V (INT) | V  | n  | V    |

| READ SECTORS                        | 08                               | V   | V  | V   | V   | V (BLK) | V  | V  | V    |

| WRITE SECTORS                       | 0A                               | V   | V  | V   | V   | V (BLK) | V  | n  | V    |

| SEEK                                | OB                               | V   | V  | V   | DR  | n       | V  | n  | V    |

| INITIALIZE DRIVE<br>PARAMETERS      | 0C                               | V   | n  | n   | 'n  | n       | n  | n  | n    |

| READ ECC BURST<br>ERROR LENGTH      | 0D                               | V   | n  | n   | n   | n       | n  | n  | n    |

| READ SECTOR BUFFER                  | 0E                               | n   | n  | n   | n   | n       | n  | n  | n    |

| WRITE SECTOR BUFFER                 | 0F                               | n   | n  | n   | n   | n       | n  | n  | n    |

| EXECUTE SECTOR<br>BUFFER DIAGNOSTIC | EO                               | n   | n  | n   | n   | n       | n  | n  | n    |

| EXECUTE DRIVE<br>DIAGNOSTIC         | E3                               | V   | n  | n   | n   | n       | v  | n  | V    |

| EXECUTE CONTROLLER<br>DIAGNOSTIC    | E4                               | n   | n  | n   | n   | n       | n  | n  | n    |

| READ LONG                           | E5                               | V   | V  | V   | V   | V (BLK) | V  | n  | V    |

| WRITE LONG                          | E6                               | V   | ν  | V   | V   | V (BLK) | V  | n  | V    |

# **TABLE 5-1. COMMAND SUMMARY**

#### LEGEND:

V Must be a valid parameter.

DR Not used but must be within a valid parameter range.

- n Not used (should be 0 for future compatibility).

- INT Interleave

- BLK Block Count

#### 5.2 I/O PORT DESCRIPTION

There are four contiguous I/O ports addressed 320 hexidecimal through 323 hexidecimal. Each port is bi-directional. The functions of the I/O

ports are listed in Table 5-2. These ports are used for all communication between the Host and Controller.

| ADDRESS | READ PORT FUNCTION            | WRITE PORT FUNCTION                      |

|---------|-------------------------------|------------------------------------------|

| 320     | READ DATA                     | WRITE DATA                               |

| 321     | READ WD1002S-WX2 HRDWR STATUS | WD1002S-WX2 RESET*                       |

| 322     | READ DRIVE CONFIGURATION INFO | WD1002S-WX2 SELECT                       |

| 323     | Not Used                      | WRITE DMA AND INTERRUPT MASK<br>REGISTER |

#### TABLE 5-2. I/O PORT DESCRIPTIONS

#### **\*NOTE**

The WD1015-14 automatically executes self-tests after either a Reset command or upon power-up. The WD1015-24 **DOES NOT** automatically execute self-test after either a Reset command or upon power-up. A WD BIOS performs an Execute Controller Diagnostic command as part of the install sequence after power-up regardless of the version of WD1015 on-board. If the Host software interrogates WD1015-24 after a Reset; the WD1015-24 returns good status. The Host must issue an Execute Controller Diagnostic command to perform the WD1015-24 self-test.

#### 5.2.1 PORT 320

This is a bi-directional path over which data, commands, parameters, and status are passed.

#### 5.2.2 PORT 321

The Host reads this port to interrogate the hardware status. This status byte can be read at any time, including command exeuction. The status bits are identified in Table 5-3.

**TABLE 5-3. HARDWARE STATUS**

| BIT |   |     |     |     |     |     |     |  |

|-----|---|-----|-----|-----|-----|-----|-----|--|

| 7   | 6 | 5   | 4   | 3   | 2   | 1   | 0   |  |

| d   | d | IRQ | DRQ | BSY | C/D | 1/0 | REQ |  |

d

Not used.

IRQ Interrupt Request. Assertion (set to 1) signifies that an interrupt is pending.

DRQ DMA request bit. Assertion (set to 1) signals the Host that the WD1002S-WX2 is ready for a DMA transfer to take place. The direction of the transfer is defined by the I/O bit.

BSY Busy bit. Assertion (set to 1) signals the Host that the WD1002S-WX2 is busy executing a command and is unable to accept another command.

C/D Control/Data. Tells the Host which type of transfer the WD1002S-WX2 is expecting. 0 = a command or status byte, 1 = data.

I/O Input/Output. Identifies the direction of transfers between the Host and WD1002S-WX2. The terms input and output are relative to the Host. 1 = input, 0 = output.

REQ Request bit. A handshake signal for data transfers between the Host and WD1002S-WX2. The WD1002S-WX2 asserts (sets to 1) this bit when it is ready for data to be transferred between it and the Host. **REQ must be valid for** every byte transferred to the Host.

The Host writes to this port to generate a MR (Master Reset) on the WD1002S-WX2. When writing to this port, the data byte is ignored.

Resetting a WD1002S-WX2 with a WD1015-14 causes automatic execution of a self-test. Automatic execution of self-test does not occur with the WD1015-24. If the Host software interrogates WD1015-24 after a Reset; the WD1015-24 returns good status. The Host must issue an execute Controller Diagnostic command to perform the WD1015-24 self-test.

#### 5.2.3 PORT 322

Reading Port 322 returns a 4-bit drive configuration code in bits 0 through 3. The two least significant bits correspond to drive 1, the two most significant bits to drive 0. The configuration of these bits is established with jumpers on the controller at SW1. Western Digital sets the configuration jumpers to one. Section 7 shows how to set them up for a specific drive.

The two bits associated with each drive is capable of addressing one of four different configuration tables. Both drives can address the same or different tables. The table required by the drive is determined by its formatted capacity. Table 0 = 5MB, 1 = 24MB, 2 = 15MB, 3 = 10MB (default table) with 62-000042-01 and 62-000042-11 WD BIOS. Table 0 = 20MB, Table 1 = 10MB, Table 2 = 20MB, Table 3 = 10MB (default table) with 62-000042-12 WD BIOS.

The parameters established by these tables are:

Number of Cylinders

- Number of Heads

- The Starting Cylinder for RWC (Reduced Write Current).

The Starting Cylinder for Write Precomp Maximum Correctable Error Burst Length Retries Allowed, Stable or Immediate ECC Correction, Step Rate.

Writing to port 322 selects the WD1002S-WX2, sets the Busy bit in the Status Register and prepares it to receive a command. When writing to port 322, the data byte is ignored.

#### 5.2.4 PORT 323

Reading this port has no function.

Writing to this port controls the enabling of the interrupt and DMA request signals to the Host. The bits in this port are defined as follows:

| BIT |   |   |   |   |   |       |       |  |

|-----|---|---|---|---|---|-------|-------|--|

| 7   | 6 | 5 | 4 | 3 | 2 | 1     | 0     |  |

| d   | d | d | d | d | d | IRQEN | DRQEN |  |

- IRQEN Interrupt Request Enable. When asserted (set to one), enables interrupts to the Host.

- DRQEN DMA Request Enable. When asserted (set to one), enables DMA requests to the Host.

- d Not used.

#### 5.3 COMMAND BLOCK

The Host first selects the WD1002S-WX2 by asserting I/OW while at the same time addressing port 322 with the A0 through A19 address bus. The WD1002S-WX2 then asserts the BSY (BUSY) bit in the Status Register. The Host by asserting  $\overline{I/OR}$ and addressing port 321 reads the status, finding REQ asserted transmits the first byte of the six byte Command Block to the WD1015. REQ is de-asserted for the second byte of the Command Block transfer. Assertion and de-assertion of REQ must occur for each byte transferred. Figure 5-1 defines the bytes within the Command Block, Table 5-1 is a summary of the commands, Section 6 Theory of Operation explains the hand shake between the Host and WD1002S-WX2 while loading the Command Block in the WD1015.

|      |                        | BITS                      |   |               |   |    |    |    |

|------|------------------------|---------------------------|---|---------------|---|----|----|----|

| BYTE | 7                      | 6                         | 5 | 4             | 3 | 2  | 1  | 0  |

| 0    |                        | OP CODE                   |   |               |   |    |    |    |

| 1    | 0 0 D HEAD NUMBER      |                           |   |               |   |    | 7  |    |

| 2    | CYLINDER<br>NUMBER MSB |                           |   | SECTOR NUMBER |   |    |    | ĒR |

| 3    |                        | CYLINDER NUMBER LSB       |   |               |   |    |    |    |

| 4    | BL                     | BLOCK COUNT OR INTERLEAVE |   |               |   |    |    |    |

| 5    | R1                     | R2                        | 0 | 0             | 0 | SP | SP | SP |

#### **FIGURE 5-1. COMMAND BLOCK DESCRIPTION**

OP Code:

Operation Code identifies the type and function of the command. Bits 7, 6, and 5 designate whether the command is operational (0) or diagnostic (E). Bits 4 through 0 select the function of the command, i.e. Read, Write, etc.

### NOTE

The WD1015-24 firmware ignores bit four of byte 0 (op code).

D

Drive number, selects one of two

drives zero or one.

Head Number Designates the head to be used on the selected drive. 0 through 15. Selection of heads eight through 15 requires WD1015-24.

#### Cylinder Number MSB and LSB Sector Number

**Block Count** or Interleave Designates the cylinder containing the sector(s) to be used by the command. 0 through 1024.

Specifies the starting sector used by the command.

Block count specifies the number of sectors to be used by a Read, Write, Read Long, or Write Long command. A block count of zero equals 256 sectors. Interleave is used by the Format commands. The maximum interleave is equal to the sectors-per-track minus one. (See Section 5.7.2 for an explanation of interleaving.)

General disk error retry disable bit. R1 controls the retry for all errors except a Data ECC error. With R1 asserted the WD1002S-WX2 makes no attempt to retry an error operation. Instead it aborts the command and sets the appropriate status in the Status Register. Because the disk is soft sectored an ID field error may cause the WD1002S-WX2 to retry for two disk revolutions. With R1 de-asserted, the WD 1002S-WX2 retries the operation for ten disk revolutions before aborting the command and setting the status bit. In the case of an ID Not Found Error the WD1002S-WX2 does a restore to track zero and seeks back to the desired track after the first ten disk revolutions and retries for ten disk revolutions before aborting and setting the error status.

ECC Error retry bit. With R2 = 1an attempt is made to correct the error on the first syndrome. R2 = 0 there must be two consecutive like syndromes before an attempt is made to correct the error.

The Step Code is used to select the rate at which step pulses are issued to the drive. Table 5-4 defines the rates corresponding to each step pulse code.

#### **TABLE 5-4. STEPPING RATE CODES**

| BITS |   | S | STEPPING RATES    |                   |  |  |  |  |

|------|---|---|-------------------|-------------------|--|--|--|--|

| 2    | 1 | 0 | WD1015-14         | WD1015-24         |  |  |  |  |

| 0    | 0 | 0 | 3 msec. per step* | 3 msec. per step* |  |  |  |  |

| 0    | 0 | 1 | 3 msec. per step  | 45µsec. per step  |  |  |  |  |

| 0    | 1 | 0 | 3 msec. per step  | 60µsec. per step  |  |  |  |  |

| 0    | 1 | 1 | 3 msec. per step  | 18µsec. per step  |  |  |  |  |

| 1    | 0 | 0 | 200µsec. per step | 210µsec. per step |  |  |  |  |

| 1    | 0 | 1 | 70µsec. per step  | 75µsec. per step  |  |  |  |  |

| 1    | 1 | 0 | 3 msec. per step  | 30µsec. per step  |  |  |  |  |

| 1    | 1 | 1 | 3 msec. per step  | 18µsec. per step  |  |  |  |  |

\* This is the preferred 3 msec. step code.

#### 5.4 TEST DRIVE READY

(CLASS 0, OP CODE 00)

This command selects the drive specified by the DRV bit in the Command Block and interrogates the DRDY, WF, and SC signals returned by that drive. If  $\overline{WF}$  and  $\overline{SC}$  are de-asserted and  $\overline{DRDY}$ asserted, the command returns an error code of 00 No Error Detected.

#### 5.4.1 POSSIBLE ERROR CODES

03 Write Fault 08 Drive Still Seeking 04 Drive Not Ready

#### 5.5 RECALIBRATE

(CLASS 0, OP CODE 01)

This command moves the Read/Write heads to track 0. The  $\overline{SC}$  signal from the drive controls the stepping rate of this command. Therefore, this command is slower than commands that implement the implied seek and make use of the stepping rate designated by the SP bits in the Command Block.

#### NOTE

5-4

Timeout on each step during a Recalibrate command is 1 second with a WD1015-14. Timeout on each step during a Recalibrate is 3.5 seconds with a WD1015-24. The 3.5 second timeout supports removable Winchesters.

## 5.5.1 POSSIBLE ERROR CODES

03 Write Fault

04 Drive Not Ready 06 Track Zero Not Found

R2

#### 5.6 <u>READ STATUS OF LAST OPERATION</u> (CLASS 0, OP CODE 03)

Upon termination of a command the WD1002S-WX2 develops a Command Completion Byte, deasserts the BSY bit, and if IRQEN had been enabled, asserts IRQ5. If IRQEN had<sup>\*</sup> not been asserted, it is the responsibility of the Host to read port 321 to determine that the WD1002S-WX2 is no longer busy. Once the Host determines that a command has terminated, it must read the Command Completion Byte to learn which drive has terminated and whether an error had occurred. To do this the Host reads port 320. The format of the Command Completion Byte is as follows:

| BIT |   |   |   |   |   |   |   |  |

|-----|---|---|---|---|---|---|---|--|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| 0   | 0 | D | 0 | 0 | 0 | Е | 0 |  |

D = Number of the drive terminating. 0 = drive 0. 1 = drive 1. E = 1 if an error occurred.

If the Command Completion Byte indicates the occurrence of an error, issue a Read Status command for the drive indicating the error. Performance of a Read Status command before any other command execution prevents loss of the error status. When a Read Status of the last operation is written to port 320 the WD1002S-WX2 responds with four bytes of status as shown in Figure 5-2.

|      |                     | BITS                                 |               |   |   |   |    |   |  |

|------|---------------------|--------------------------------------|---------------|---|---|---|----|---|--|

| BYTE | 7                   | 6                                    | 5             | 4 | 3 | 2 | 1  | 0 |  |

| 0    | AV                  | 0                                    | ERROR CODE    |   |   |   |    |   |  |

| 1    | 0                   | 0                                    | D HEAD NUMBER |   |   |   |    | 7 |  |

| 2    |                     | CYLINDER<br>JUMBER MSB SECTOR NUMBER |               |   |   |   | ĒR |   |  |

| 3    | CYLINDER NUMBER LSB |                                      |               |   |   |   |    |   |  |

AV Address valid bit. Indicates that the Head, Cylinder, and Sector fields are valid.

Error Codes are shown in Table 5-5.

All other bits are the same as those defined in the Command Block definitions.

#### **FIGURE 5-2. FOUR STATUS BYTES**

When an error occurs during a multiple sector data transfer (read or write), this command returns the address of the failing sector. If the Read Status command is issued after any of the format commands or the Verify Desired Sectors command, the address returned by the WD1002S-WX2 points one sector beyond the last track formatted or checked, if there was no error. If there was an error, then the address returned points to the track in error.

| HEX  | DEFINITION                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE | DEFINITION No error detected.                                                                                                                                                                                                                                              |

| 00   |                                                                                                                                                                                                                                                                            |

| 02   | No $\overline{SC}$ signal from the drive. The WD1002S-WX2 has not received a $\overline{SC}$ from the drive within one second (3.5 seconds with WD1015-24) following the last step pulse of a non-buffered seek operation.                                                 |

| 03   | Write Fault signal received from the drive. This error is reported when the WD1002S-WX2 detects $\overline{WF}$ asserted by a drive either at the completion of a Sector Data Transfer or after initially selecting a drive and the drive indicates ready.                 |

| 04   | Drive Not Ready. The WD1002S-WX2 reports this error when $\overline{\text{DRDY}}$ is not received from the drive at the time selection is attempted, or is de-asserted after the drive has been selected.                                                                  |

| 06   | Track 0 Not Found. This error is reported during a Recalibrate command if $\overline{TK000}$ is not received from the drive before stepping the Read/Write Heads 1024 steps.                                                                                               |

| 08   | Drive Still Seeking. This status is returned in response to a Test Drive Ready command when a drive performing a buffered seek has not yet asserted SC.                                                                                                                    |

| 11   | Uncorrectable Data Error. The ECC logic detected an error burst greater than its correction capabilities. The data in the Sector Buffer is not sent to the Host.                                                                                                           |

| 12   | Data Address Mark Not Found. The proper Sector ID was read by the drive but failed to detect the Data Address Mark.                                                                                                                                                        |